# SF32LB52x

big.LITTLE Arm Cortex-M33 STAR-MC1@192MHz/24MHz, 787 CoreMark 2D/2.5D GPU, 576KB SRAM, BT/BLE 5.3

## **Product Brief**

#### **Key Features**

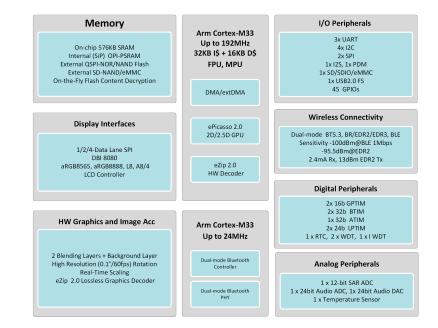

- Bluetooth MCU with dual-core Arm Cortex-M33 STAR-MC1 up to 192MHz/24MHz, 787 Core-Mark, 370 DMIPS, suitable for both feature-rich graphical HMI and ultra-low power sensor hub operation

- ePicasso<sup>™</sup>2.0 2D/2.5D GPU, support rotation and scaling

- eZip<sup>™</sup>2.0 lossless graphics decompression, support native animation

- Dual-mode BT5.3, EDR2 sensitivity of -95.5dBm, BLE 1Mbps sensitivity of -100dBm and Rx power of 2.4mA@3.8V

- HiFi audio ADC/DAC, support audio playback and Bluetooth call

- 576KB on-chip SRAM, support (SiP) OPI-PSRAM, interfaces for NOR, NAND, and eMMC

- Support lithium battery power supply, integrated charging, Max. charging current 560mA;

2 external 3.3V power supply LDOs, Max. load current 150mA×2

- QFN68L, up to 45 GPIOs

#### Applications

- Smart watch

- Activity and fitness monitor

- Graphical HMI device

- Smart home appliance

- Low-power sensor hub

SF32LB52x is a family of highly integrated high-performance MCUs for ultra-low power AIoT scenarios. It adopts a big.LITTLE architecture based on Arm Cortex-M33 STAR-MC1 processor, and is embedded with 2D/2.5D GPU, dual-mode BT5.3, and audio codec. SF32LB52x can be used for a wide variety of applications such as smart wearables, smart HMI devices, and smart home, etc.

The big core high performance application processor can operate at up to 192MHz for 787 CoreMark. The low-power processor serves as both sensor hub and Bluetooth controller at high energy efficiency of 4.8uA/CoreMark. This architecture delivers no-compromise user experience of both high performance computing required for featurerich graphical HMI and ultra-low power sensor hub operation.

The 2D/2.5D GPU, at up to 192MHz, support 2-layer alpha blending, hardware accelerated rotation and scaling, and conversion of various common graphic formats.  $eZip^{TM}2.0$  supports lossless compressed graphics file, saving memory bandwidth and storage capacity. The LCD controller can support interfaces of 8080/QSPI at a full-screen refresh frame rate up to 60fps, and support Always-On Display.

The world-class dual-mode BT5.3 transceiver has a maximum Tx power of 13dBm at EDR2 mode and Rx power of 2.4mA@3.8V, and the sensitivity reaches -100dBm (1Mbps) for BLE and -95.5dBm for EDR2.

PB0052-SF32LB52x-EN (V0.9)

# SF32LB52x

### **Product Brief**

#### **CPU and Memory**

- High Performance Application Processor (HCPU)

- Arm Cortex-M33 STAR-MC1

- Clock up to 192MHz, adjustable

- Up to 296DMIPS, 787 EEMBC CoreMark

- I-Cache + D-Cache: 32KB(2-way)+16KB(4-way)

- SRAM: 512KB (All Retention SRAM)

- CoreMark power: 23uA/MHz @3.8V

- Single Precision Floating Point Unit (FPU)

- Memory Protection Unit (MPU)

- Ultra Low-Power Processor (LCPU)

- Arm Cortex-M33 STAR-MC1

- Clock up to 24MHz, adjustable

- SRAM: 64KB (All Retention SRAM)

#### **Wireless Connectivity**

- Dual-mode BT5.3, support BLE Audio

- Sensitivity: -100dBm(BLE/1Mbps), -96.3dBm(BR), -95.5dBm(EDR2)

- Max. Tx power: 13dBm (EDR2/3), 19dBm (BR/BLE)

- Rx peak current (BR): 2.4mA@3.8V

#### Audio

- 1×HiFi 24-bit Audio DAC, 109dB SNR

- 1×HiFi 24-bit Audio ADC, 99dB SNR

#### **Graphics and Display**

- 2D/2.5D GPU—ePicasso<sup>™</sup>2.0

- Hardware-accelerated rotation, scaling, and mirroring

- Max. resolution:  $512 \times 512$

- Support aRGB8565, aRGB8888, L8, A8/4/2,YUV, support alpha blending

- Lossless Decompression Accelerator eZip<sup>™</sup>2.0

- Lossless graphics decompression

- support native animation eZip-A

- Concatenated operation with ePicasso<sup>™</sup>2.0

- LCD Controller

- Support 8080, SPI, Dual-SPI, Quad-SPI

- 1 layer + 1 background layer alpha blending

- Independent LCD controller, Always-On Display

#### **Memory Interface**

- Support (SiP) OPI-PSRAM, interface frequency up to 144MHz

- 1×MPI(QSPI), support NOR, NAND, QPI-PSRAM

- 1×SD/SDIO, support SD3.0, SDIO3.0, eMMC

#### Others

- DMA

- General DMA: high efficiency data transfer between internal memory and peripherals

- extDMA: high efficiency data transfer between internal memory and external memory

- Security

- AES, HASH and CRC hardware accelerators

- True random number generator (TRNG)

- PSA Certified Level 1

- Timers

- $2 \times 16b$  GPTIM,  $2 \times 32b$  BTIM,  $1 \times 32b$  ATIM

- 2×24b LPTIM

- $1 \times RTC$ ,  $2 \times 24b$  WDT,  $1 \times IWDT$

- Analog Peripherals

- 1×12-bit general purpose SAR ADC, 8 channels

- 1×Temperature sensor

- I/O Peripherals

- Up to 45 GPIOs

- 3×UART, 4× I $^{2}$ C, 2×SPI, 1× I $^{2}$ S, 1× PDM

- 1×USB2.0 FS

- Peripheral Task Controller (PTC)

- Power Management

- High-efficiency buck and low-power LDO

- 2 external 3.3V power supply LDOs, Max. current 150mA×2

- Sleep current: 2uA

- Built-in 560mA lithium battery linear charger, supporting 4.2V-4.45V full voltage

- VBAT voltage range: 3.2V-4.7V

- VBUS voltage range: 4.6V-5.5V

#### Package

• QFN68L, 45 GPIOs, 7×7×0.85mm